在复杂电子设备设计中,晶振与开关电源的频率选择绝非小事。当多个同频器件共存时,其基频与谐波的叠加会显著放大EMI噪声,使设备面临超标风险。本文将探讨如何通过频谱分配策略从源头优化电磁兼容性。

问题核心:同频叠加效应

- 归一化采购的陷阱:为简化采购选用同规格晶振或DCDC开关频率,导致同频基波和谐波能量叠加,辐射噪声增强。

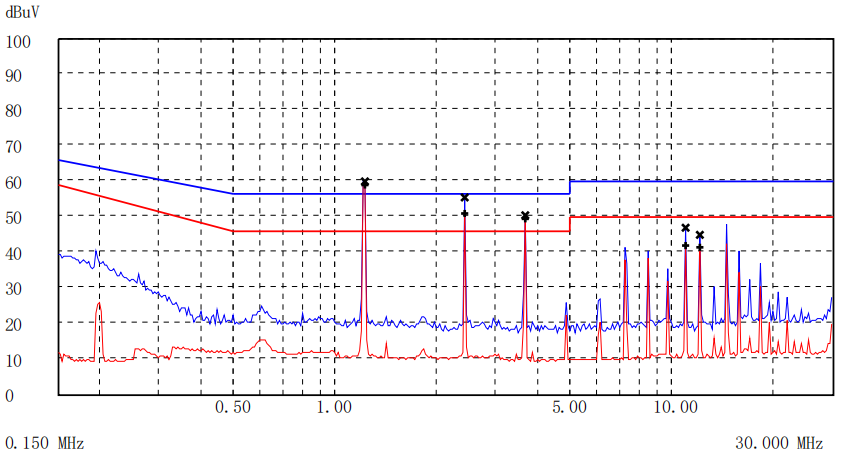

- 频谱分配的价值:有意识错开工作频率,分散噪声能量,即使频点数量增加,但单点强度显著降低,更易满足EMC要求。

晶振频率选择策略:奇偶谐波的艺术

案例场景:主板上已使用8MHz晶振,另一板卡需新增晶振,可选8MHz、16MHz或24MHz。

- 淘汰同频(8MHz):基波与谐波直接叠加,噪声强化风险最高。

- 谐波特性关键点:50%占空比方波的偶次谐波理论为零(依据傅里叶变换)。

- 频谱分析:

- 16MHz & 8MHz:16M (基波) → 48M (3次), 80M (5次)…;8M → 24M (3次), 40M (5次)… —— 关键奇次谐波完美错开。

- 24MHz & 8MHz:24M (基波) → 72M (3次), 120M (5次)…;8M → 24M (3次), 72M (9次)… —— 在24MHz、72MHz等频点重叠。

- 结论:优选16MHz与8MHz组合。设计准则:避免晶振频率成奇数倍关系(如3倍、5倍)。

DCDC电源的特殊挑战

- PWM占空比动态变化:几乎不可能稳定在50%,导致奇次与偶次谐波均存在。

- 频率选择原则:严格规避

fk1 = n * fk2(或fk2 = n * fk1)的整数倍关系(无论n奇偶),防止基波及所有谐波分量叠加。

典型案例:125MHz晶振与500MHz辐射

- 问题:RE测试中500MHz频点超标,恰为125MHz晶振的4倍频。

- 误区分析:试图通过滤波125MHz抑制500MHz辐射。

- 核心机制:125MHz信号输入PHY芯片后,内部电路进行2^n次倍频(此例中为4倍频),生成全新的500MHz强信号。

- 解决方案:

- 源头处理:在PHY芯片的500MHz输出端加强滤波、屏蔽或布局优化。

- 频谱规划:若可能,避免使用易被高频倍频的基频(如125MHz)。

频谱分配:系统级EMI设计的关键

- 核心思想:在架构设计阶段,全局规划关键频率源(晶振、DCDC开关频率、时钟发生器),主动分散其基波与主要谐波。

- 价值:大幅降低单点噪声强度,减少后期滤波、屏蔽等补救措施的难度和成本。

设计启示录:优秀的EMC设计始于系统规划。通过精妙的频谱分配,在信号源头化解噪声叠加危机,是打造高可靠性电子设备的基石。下一次布局晶振或设定电源频率时,不妨将频谱图纳入设计考量——这或许是最经济的EMC解决方案。