阻容复位电路的本质是上电、掉电过程复位电路。上电复位的时序与掉电复位的时序是不同的。

上电时:Vcc先上电过Vccmin——然后复位解除;

掉电时:先复位生效——然后Vcc掉到Vccmin以下。

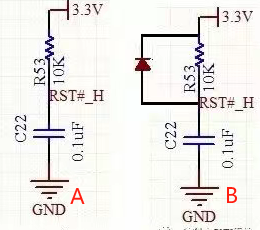

下图A电路的“上电”时序时没有问题,电阻电容充电慢,Vcc先上电稳定下来了,然后RST才由低到高,解除复位;但掉电时序时,Vcc很快掉下去了或者电压不稳,可RST还处于高电平区,未能进入复位状态,这种情况下的芯片还可能工作于工作状态,容易发生芯片损伤、闩锁、EEPROM被刷、数据传输错乱等问题。

如果对成本不是那么苛求,可以考虑采用复位芯片,芯片中把上电复位、掉电复位、电压波动导致复位的施密特触发机制都一一做了处理,可以让我们设计师在对此懵懂无知的状态下就能完成此项设计工作。

但如果对成本比较在乎,则推荐加个二极管的(图B)措施。上电过程AB原理相同,掉电时,图B通过二极管放电,虽然仍然不能快于Vcc进入复位保护状态,但相比于图A掉电还是快了不少,尤其是电阻值选得较大的时候。

时序是一个软性的设计,电路实质未发生改变,但次序的调整,就能带来生产力。铁路行业的夕发朝至曾经带来了我们多少的便利。嵌入式软件里的控制时序,广阔天地,大有可为。

还有另外一个问题,不用增加什么东西,稍微调整一下,也能带来巨大改善的指标:位置。世上没有垃圾,垃圾就是放错了位置的资源。布局、接线造成了干扰,就是放错了未知的资源。后面文章再探讨。